第5世代 AMD EPYC (Turin) 搭載「R8a」がリリース、東京リージョンでも「M8a」が利用可能になりました

2025年11月5日、メモリ最適化インスタンスファミリーである「R8a」がリリースされていました。

今回、オレゴンリージョンで「R8a」を、また先月リリースされ既に東京リージョンでも利用可能となっている「M8a」インスタンスを起動し、前世代のインスタンスとのコスト比較を行いましたので紹介させていただきます。

- Amazon EC2 R8a instances are now available(2025/11/05)

- New general-purpose Amazon EC2 M8a instances are now available (2025/10/08)

- Amazon EC2 M8a Instances now available in additional regions (2025/11/11)

EC2ダッシュボード

起動画面

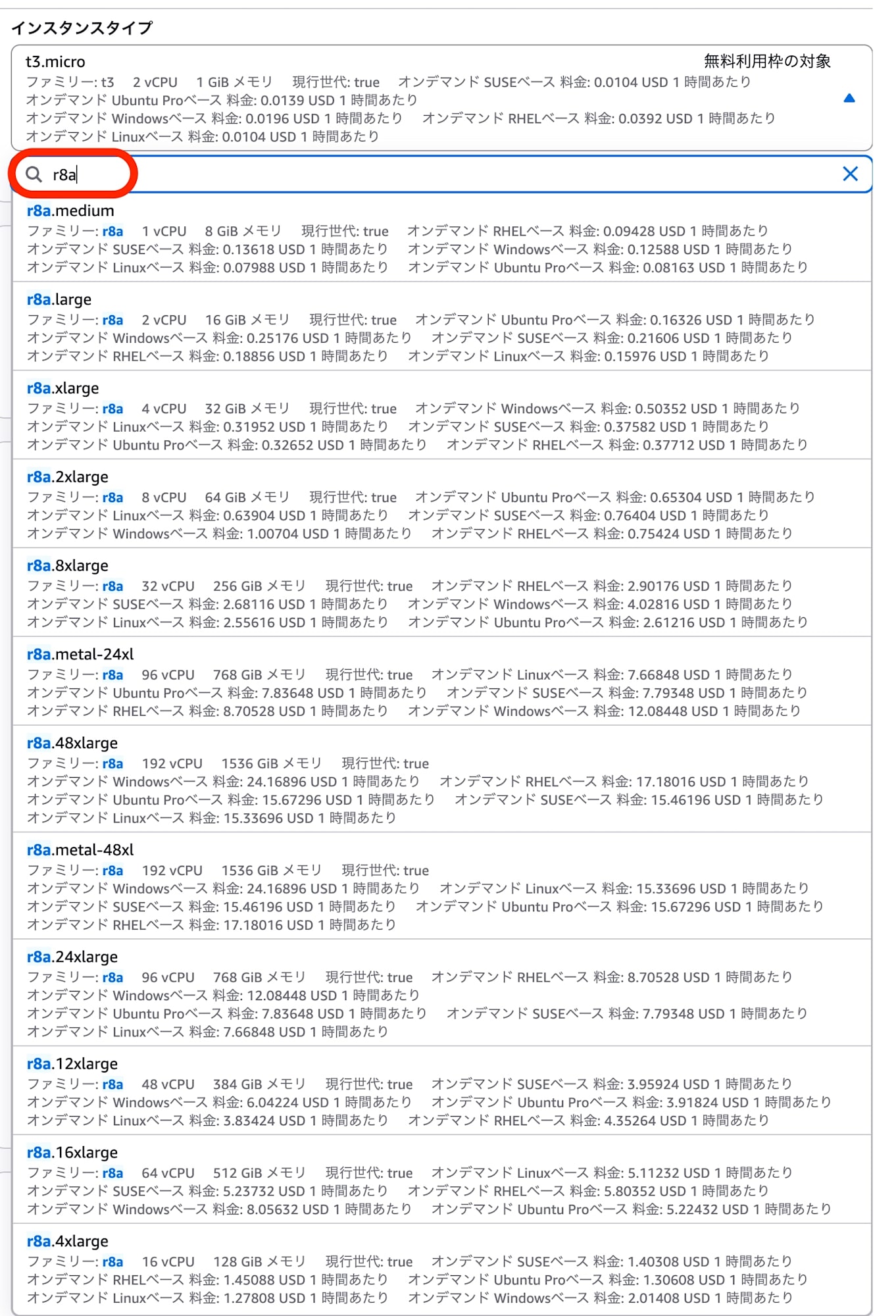

オレゴンリージョンの起動画面では、メモリ最適化の「r8a」が選択可能となっていることを確認しました。

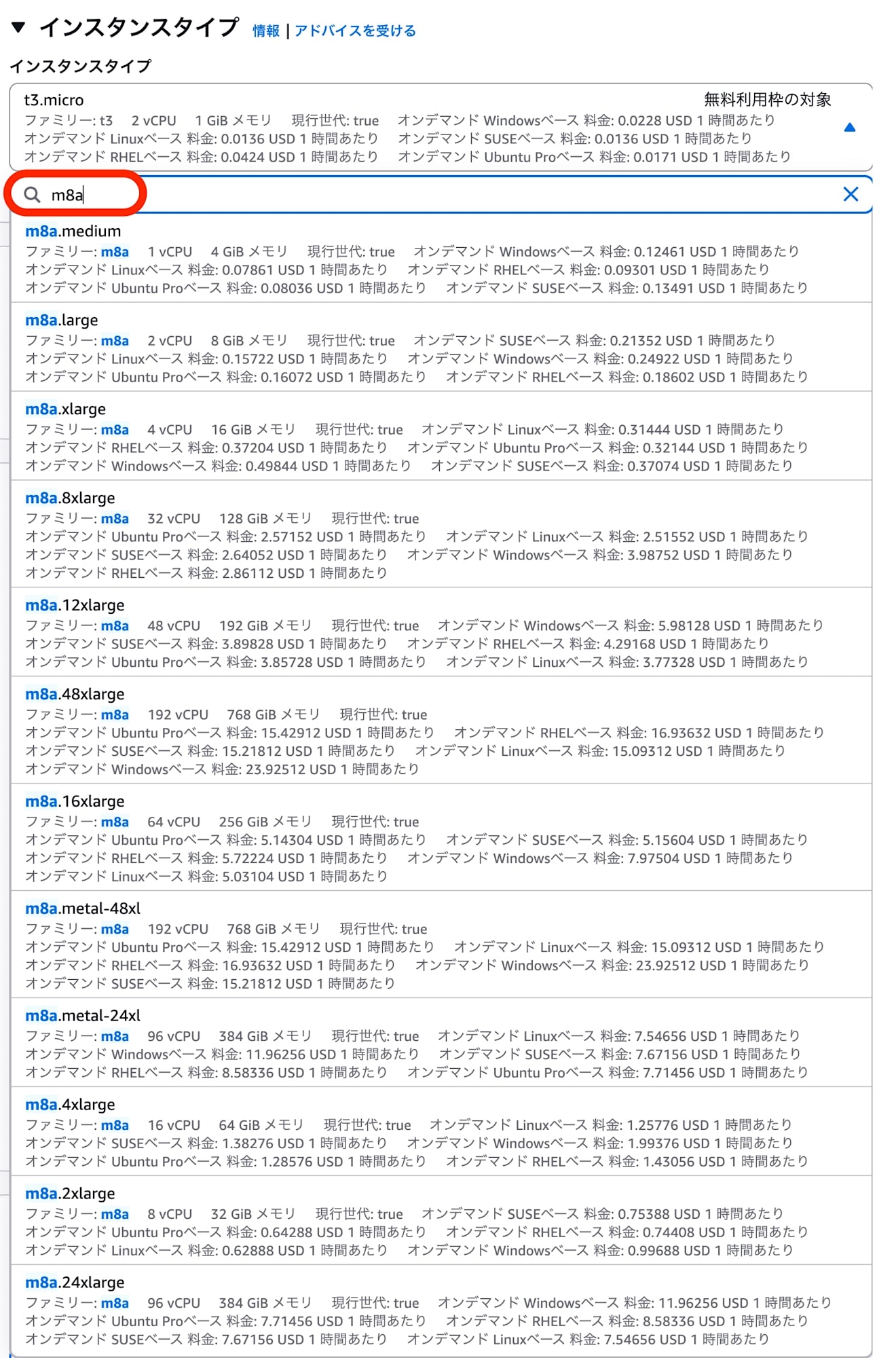

東京リージョンのEC2インスタンスの起動時、インスタンスタイプとして「m8a」の選択が可能になりました。

インスタンスタイプ情報

第 5 世代 AMD EPYC プロセッサ (Turin) を搭載した以下のインスタンスファミリーが確認できました。

M8a については、2025年11月12日より東京リージョンでも利用可能となっています。

R8a (メモリ最適化) 利用可能リージョン

- us-east-1 (バージニア北部)

- us-east-2 (オハイオ)

- us-west-2 (オレゴン)

M8a (汎用) 利用可能リージョン

- us-east-1 (バージニア北部)

- us-east-2 (オハイオ)

- us-west-2 (オレゴン)

- ap-northeast-1 (東京) ※2025/11/12 追加

lscpu

r8a.medium をオレゴンリージョンで起動。lscpu で搭載CPU情報を確認しました。

CPUのモデルは「AMD EPYC 9R45」でした。M8aについても同一のプロセッサが採用されています。

sh-5.2$ lscpu

Architecture: x86_64

CPU op-mode(s): 32-bit, 64-bit

Address sizes: 48 bits physical, 48 bits virtual

Byte Order: Little Endian

CPU(s): 1

On-line CPU(s) list: 0

Vendor ID: AuthenticAMD

Model name: AMD EPYC 9R45

CPU family: 26

Model: 2

Thread(s) per core: 1

Core(s) per socket: 1

Socket(s): 1

Stepping: 1

BogoMIPS: 5199.99

Flags: fpu vme de pse tsc msr pae mce cx8 apic sep mtrr pge mca cmov pat pse36 clflush mmx fxsr sse sse2 syscall n

x mmxext fxsr_opt pdpe1gb rdtscp lm constant_tsc rep_good nopl nonstop_tsc cpuid extd_apicid aperfmperf tsc

_known_freq pni pclmulqdq monitor ssse3 fma cx16 pcid sse4_1 sse4_2 x2apic movbe popcnt aes xsave avx f16c

rdrand hypervisor lahf_lm cr8_legacy abm sse4a misalignsse 3dnowprefetch topoext perfctr_core invpcid_singl

e ssbd perfmon_v2 ibrs ibpb stibp vmmcall fsgsbase bmi1 avx2 smep bmi2 invpcid avx512f avx512dq rdseed adx

smap avx512ifma clflushopt clwb avx512cd sha_ni avx512bw avx512vl xsaveopt xsavec xgetbv1 xsaves avx512_bf1

6 clzero xsaveerptr rdpru wbnoinvd arat avx512vbmi pku ospke avx512_vbmi2 gfni vaes vpclmulqdq avx512_vnni

avx512_bitalg avx512_vpopcntdq rdpid flush_l1d

Virtualization features:

Hypervisor vendor: KVM

Virtualization type: full

Caches (sum of all):

L1d: 48 KiB (1 instance)

L1i: 32 KiB (1 instance)

L2: 1 MiB (1 instance)

L3: 4 MiB (1 instance)

NUMA:

NUMA node(s): 1

NUMA node0 CPU(s): 0

注目すべき仕様の変化

lscpu の出力から、以下の技術的な変更点が確認できました。

- CPU Family 26 (Zen 5):

CPU family: 26は Zen 5 アーキテクチャを示しています(前世代の Genoa は Family 25)。 - L1d キャッシュの増量:

L1d cacheが 48 KiB となっています。前世代(R7a/M7a)の 32 KiB から 1.5倍 に増量されており、キャッシュヒット率の向上が期待されます。 - AI推論向け命令セット:

avx512_bf16やavx512_vnniフラグが確認でき、CPU単体でのAI推論処理能力が強化されています。

コスト比較

最新の第 8 世代 (Turin) と 第 7 世代 (Genoa) のLinuxインスタンス利用時、R8a と R7a のオンデマンド価格を比較しました。

r8a/r7a

| タイプ | vCPUs | Memory (GiB) | R8a (USD) | R7a (USD) |

|---|---|---|---|---|

| medium | 1 | 8 | 0.0799 | 0.0761 |

| large | 2 | 16 | 0.1598 | 0.1522 |

| xlarge | 4 | 32 | 0.3195 | 0.3043 |

| 2xlarge | 8 | 64 | 0.6390 | 0.6086 |

| 4xlarge | 16 | 128 | 1.2781 | 1.2172 |

| 8xlarge | 32 | 256 | 2.5562 | 2.4344 |

| 12xlarge | 48 | 384 | 3.8342 | 3.6516 |

| 16xlarge | 64 | 512 | 5.1123 | 4.8688 |

| 24xlarge | 96 | 768 | 7.6685 | 7.3032 |

| 48xlarge | 192 | 1536 | 15.3370 | 14.6064 |

| metal-48xl | 192 | 1536 | 15.3370 | 14.6064 |

※価格はUnix/Linux1時間のオンデマンド料金(USD) (オレゴンリージョン)

最新の AMD 搭載インスタンスのオンデマンド価格は、同等スペックの前世代(R7a)と比較して 約 5% 高額 な設定でした。

これまでの AMD インスタンスは新旧世代で価格が据え置かれる傾向がありましたが、今回の R8a/M8a では単価設定が上昇しています。

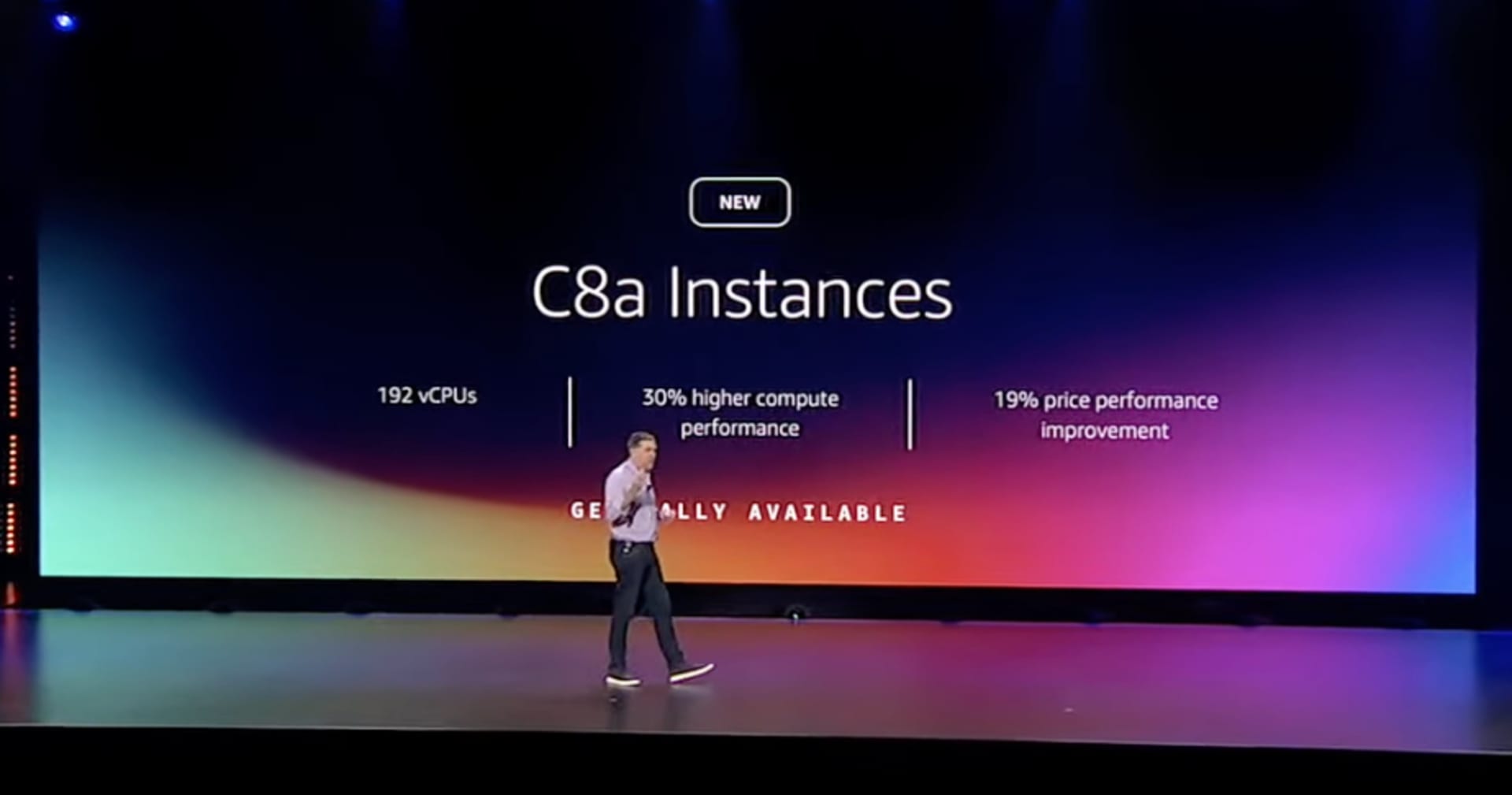

ただし、公式情報によるとパフォーマンスは最大 30% 向上しており、同じワークロードをより少ないインスタンス数で処理できる場合、実質的なコスト効率は約 19% 向上する可能性があります。

まとめ

今回オレゴンリージョンなどで利用可能となった「R8a」、および東京リージョンで利用可能となった「M8a」は、4.5 GHz の高クロック動作と、L1キャッシュの増量により、処理能力が大幅に強化されています。

最後に、Intel 製インスタンスと比較した際の重要なアーキテクチャの違いについて触れておきます。

vCPU の実体と物理コアの関係

Intel 製プロセッサを搭載した同世代のインスタンス(R7i, M7i など)では、通常ハイパースレッディング (HT) が有効化されており、2 vCPU = 1 物理コア (2スレッド) として提供されます。

一方、今回検証した R8a/M8a では、lscpu の結果 (Thread(s) per core: 1) が示す通り、1 vCPU が 1 物理コア に直接マッピングされています。

- R7i.large (2 vCPU) : 実質 1 物理コア (HT利用)

- R8a.large (2 vCPU) : 実質 2 物理コア (物理コア占有)

このため、ハイパースレッディングの効果が薄い(競合が発生しやすい)計算集約型のワークロードや、物理コアの性能をフルに引き出したいバッチ処理などにおいては、実コアを多く利用できる R8a/M8a の方が、スペック表以上の高い実効性能を発揮する可能性が高いと言えます。

単価は約 5% 上昇しましたが、メモリ帯域幅の拡大と合わせ、この「物理コア占有」の特性を理解して使い分けることで、大幅なコストパフォーマンスの改善が期待できます。